### **Instruction Set of 8085**

- An instruction is a binary pattern designed inside a microprocessor to perform a specific function.

- The entire group of instructions that a microprocessor supports is called *Instruction Set*.

- 8085 has 246 instructions.

- Each instruction is represented by an 8-bit binary value.

- These 8-bits of binary value is called *Op-Code* or *Instruction Byte*.

Gursharan Singh Tatla professorgstatla@gmail.com

www.eazynotes.com

## **Classification of Instruction Set**

- Data Transfer Instruction

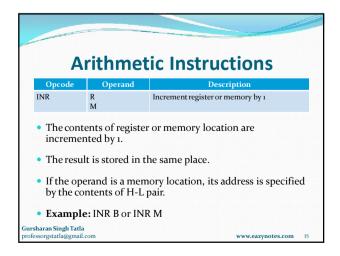

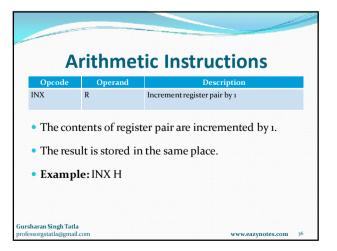

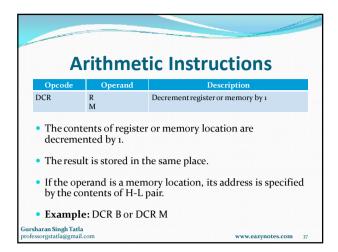

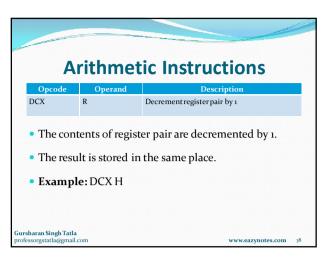

- Arithmetic Instructions

- Logical Instructions

- Branching Instructions

- Control Instructions

Gursharan Singh Tatla professorgstatla@gmail.co

ww.eazynotes

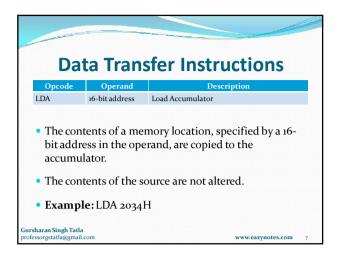

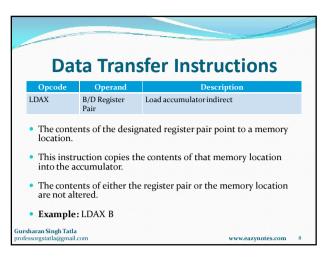

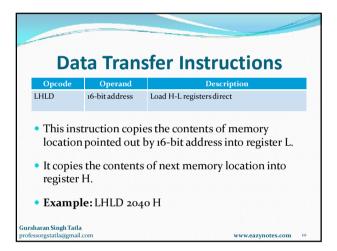

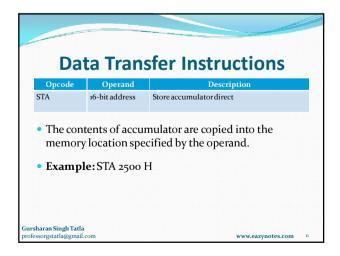

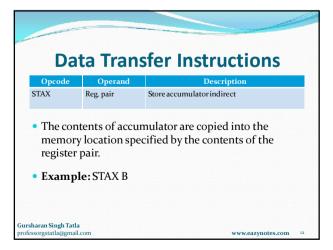

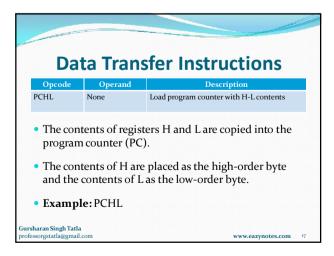

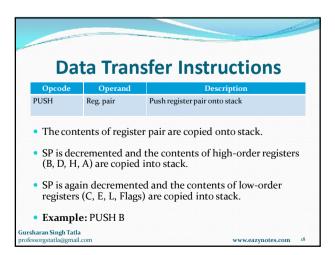

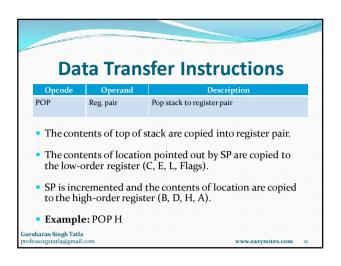

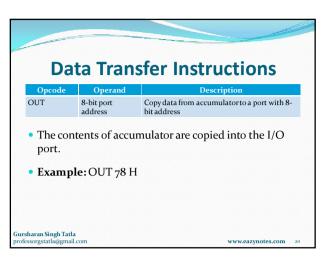

#### **Data Transfer Instructions**

- These instructions move data between registers, or between memory and registers.

- These instructions copy data from source to destination.

- While copying, the contents of source are not modified.

Gursharan Singh Tatla professorgstatla@gmail.co

www.eazynotes.com

## Opcode Operand Description MOV Rd, Rs M, Rs Rd, M Copy from source to destination. • This instruction copies the contents of the source register

- This instruction copies the contents of the source register into the destination register.

- The contents of the source register are not altered.

- If one of the operands is a memory location, its location is specified by the contents of the HL registers.

- Example: MOV B, C or MOV B, M

Gursharan Singh Tatla professorgstatla@gmail.

www.eazynotes.com 5

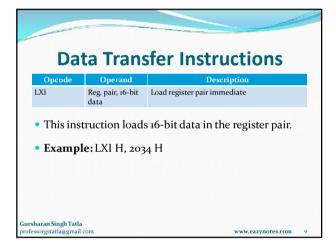

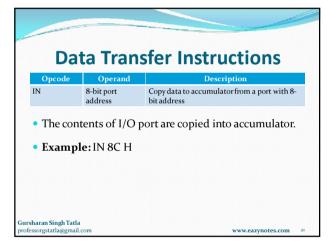

## **Data Transfer Instructions**

| Opcode | Operand             | Description          |

|--------|---------------------|----------------------|

| MVI    | Rd, Data<br>M, Data | Move immediate 8-bit |

- The 8-bit data is stored in the destination register or memory.

- If the operand is a memory location, its location is specified by the contents of the H-L registers.

- Example: MVI B, 57H or MVI M, 57H

Gursharan Singh Tatla

www.eazynotes.com

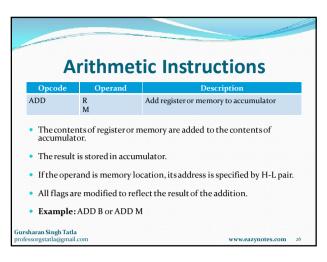

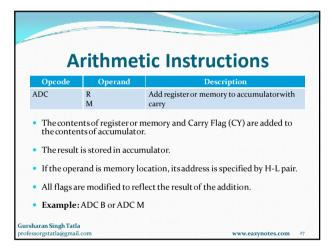

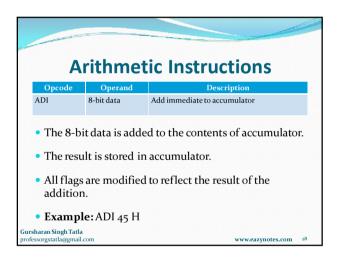

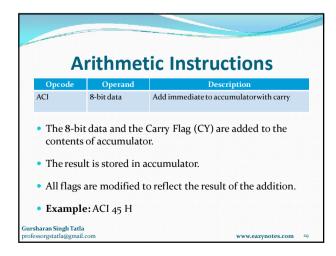

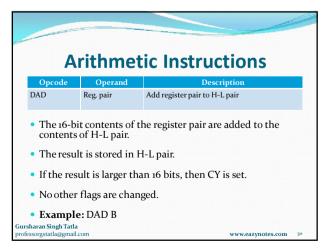

# Addition • Any 8-bit number, or the contents of register, or the contents of memory location can be added to the contents of accumulator. • The result (sum) is stored in the accumulator. • No two other 8-bit registers can be added directly. • Example: The contents of register B cannot be added directly to the contents of register C. Gursharan Singh Tatla professorgstatla@gmail.com

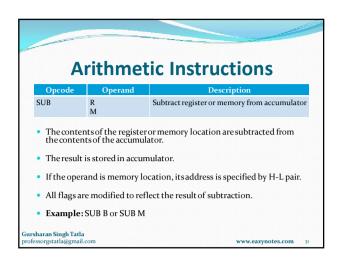

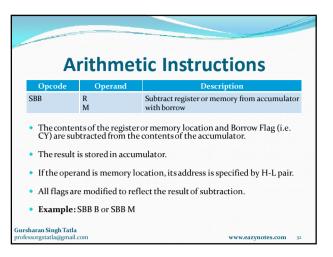

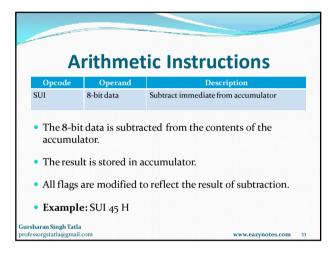

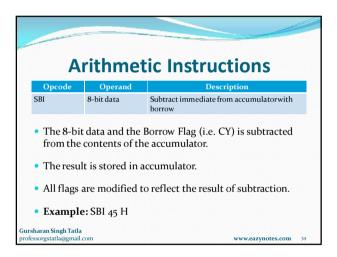

## Subtraction Any 8-bit number, or the contents of register, or the contents of memory location can be subtracted from the contents of accumulator. The result is stored in the accumulator. Subtraction is performed in 2's complement form. If the result is negative, it is stored in 2's complement form. No two other 8-bit registers can be subtracted directly.

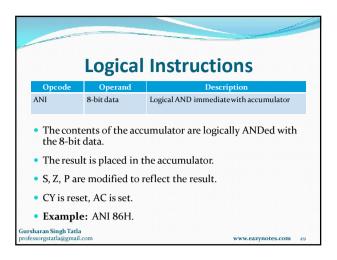

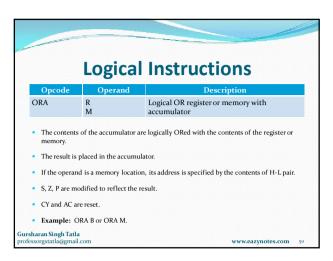

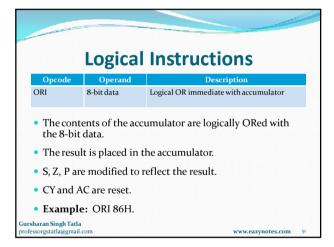

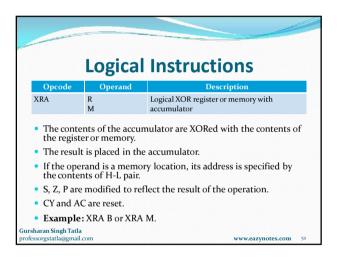

|                                                | Logical                                                 | Instructions                                    |  |  |

|------------------------------------------------|---------------------------------------------------------|-------------------------------------------------|--|--|

| Opcode                                         | Operand                                                 | Description                                     |  |  |

| ANA                                            | R<br>M                                                  | Logical AND register or memory with accumulator |  |  |

| of register                                    | nts of the accumul<br>or memory.<br>is placed in the ac | ator are logically ANDed with the contents      |  |  |

| <ul> <li>If the oper contents o</li> </ul>     |                                                         | ocation, its address is specified by the        |  |  |

| • S, Z, P are                                  | modified to reflec                                      | t the result of the operation.                  |  |  |

| <ul> <li>CY is reset</li> </ul>                | and AC is set.                                          |                                                 |  |  |

| • Example:                                     | ANA B or ANA M                                          | 1.                                              |  |  |

| ursharan Singh Tatla<br>rofessorgstatla@gmail. |                                                         | www.eazynotes.com 48                            |  |  |

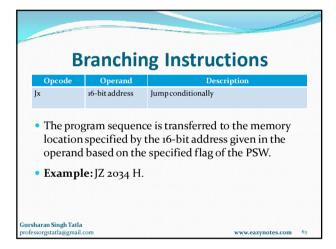

| Jump Conditionally                              |                     |                      |  |  |  |  |

|-------------------------------------------------|---------------------|----------------------|--|--|--|--|

| Opcode                                          | -                   | Status Flags         |  |  |  |  |

| JC                                              | Jump if Carry       | CY = 1               |  |  |  |  |

| JNC                                             | Jump if No Carry    | CY = o               |  |  |  |  |

| JP                                              | Jump if Positive    | S = 0                |  |  |  |  |

| JM                                              | Jump if Minus       | S = 1                |  |  |  |  |

| JZ                                              | Jump if Zero        | Z = 1                |  |  |  |  |

| JNZ                                             | Jump if No Zero     | Z = o                |  |  |  |  |

| JPE                                             | Jump if Parity Even | P = 1                |  |  |  |  |

| JPO                                             | Jump if Parity Odd  | P = o                |  |  |  |  |

| ursharan Singh Tatla<br>ofessorgstatla@gmail.co | m                   | www.eazynotes.com 64 |  |  |  |  |

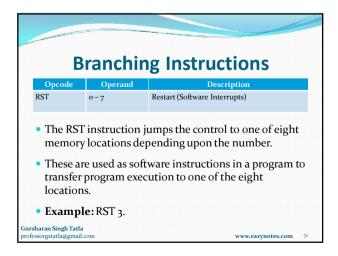

| Restart Address Table                               |                  |                 |                |  |  |

|-----------------------------------------------------|------------------|-----------------|----------------|--|--|

|                                                     | Instructions     | Restart Address |                |  |  |

|                                                     | RST o            | 0000 H          |                |  |  |

|                                                     | RST 1            | 0008 H          |                |  |  |

|                                                     | RST 2            | 0010 H          |                |  |  |

|                                                     | RST <sub>3</sub> | 0018 H          |                |  |  |

|                                                     | RST <sub>4</sub> | 0020 H          |                |  |  |

|                                                     | RST 5            | 0028 H          |                |  |  |

|                                                     | RST 6            | 0030 H          |                |  |  |

|                                                     | RST <sub>7</sub> | 0038 H          |                |  |  |

| Gursharan Singh Tatla<br>professorgstatla@gmail.com | n                | www.ea:         | zynotes.com 72 |  |  |